Logický rez

Typický logický rez sa skladá zo štyroch vzájomne sa doplňujúcich sa častí:

-Programovateľné logické tabuľky

-Reťazec rýchleho šírenia prenosu

-Multiplexory

-Registre

Programovateľná logická tabuľka LUT (look-up table) slúži k realizácii lubovoľné kombinačnej logickej funkcie. Jedná sa v podstate o pamäť typu RAM, jeho obsah je pri bežnom použití pevne nastavený konfiguračnými dátami. Realizuje teda jednu alebo dve binárne funkcie niekoľkými (typicky 4-6) vstupnými binárnými premennými. Okrem tejto základnej funkcie umožňuje LUT obvykle realizáciu i iných typov funkčných blokov ako sú malé pamäti RAM a ROM alebo posuvné registre.

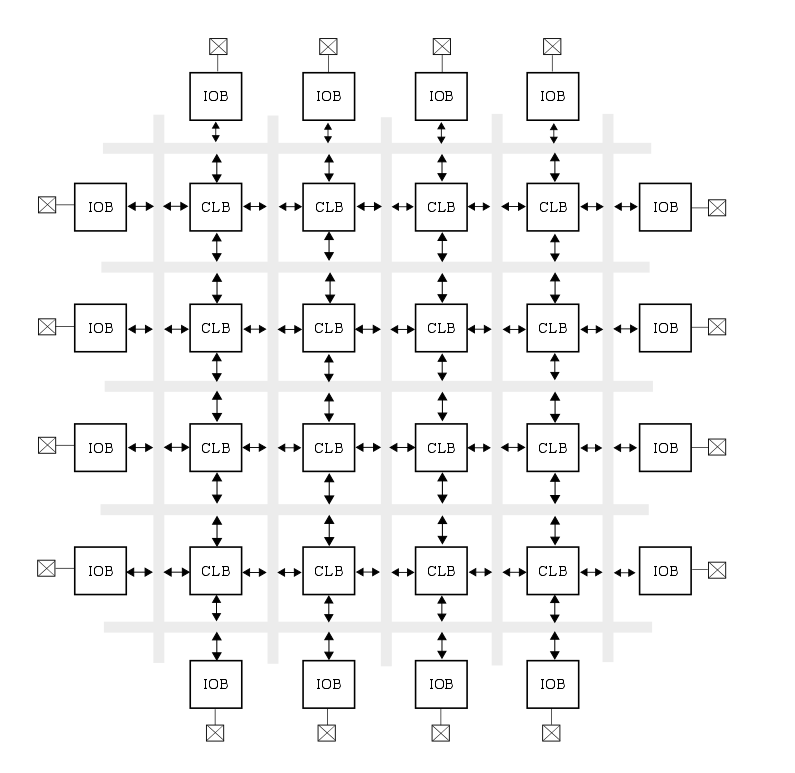

Reťazec rýchleho šírenia prenosu (carry chain) umožňuje vytvorenie rôznych aritmetických obvodov, ako sú napríklad sčítačky. Zatiaľ čo bežné vstupy a výstupy logických rezov sú pripojene k pomalej globálnej prepojovacej matici. Vstup a výstup prenosu Cin a Cout sú priamo pripojene so susednými konfigurovateľnými logickými blokmi v rovnakom stĺpci.

Programovateľné multiplexery umožňujú realizáciu logických funkcíí viacerých premenných ako je šírka jednej LUT. Funkcie sú potom realizované skombinovaním výstupov niekoľkých LUT v jednom logickom reze pomocou multiplexorov. Podobnej funkcionality je možné dosiahnuť kombináciu niekoľkých logických blokov, ale prepojenie medzi jednotlivými CLB je oveľa pomalšie ako priamy spoj medzi LUT a multiplexormi.

Registre v logických rezoch umožňujú realizáciu sekvenčných logických funkcií. Pri konfigurácii rezu je možné nastaviť vlastnosti jednotlivých registrov ako napríklad využitie clock-enable, polarita a typ set/reset vstupu a podobne. Ak používajú registre clock-enable tak musia byť pripojené k rovnakému zdroju. Nie každý register však musí clock-enable a reset používať. prípadne môže reset využívať iným spôsobom ako ostatné registre.