FPGA

FPGA možno zaradiť medzi hardvérové zabezpečenie siete. Ide o polovodičové zariadenia, ktoré sú založené na matici konfigurovateľných logických blokoch (CLB) pripojených cez programovateľné prepojenia. FPGA po výrobe nie sú naprogramované. Urobí tak používateľ podľa požiadaviek aplikácie alebo podľa funkcie požiadavky. Táto vlastnosť rozlišuje FPGA od Aplikácie špecifických integrovaných obvodov (ASIC), ktoré sú vyrábané pre špecifické konštrukčné úlohy.

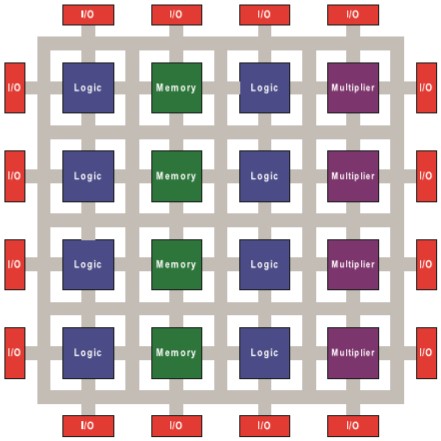

FPGA pozostávajú z radu programovateľných logických blokov rôznych typov, vrátane všeobecnej logiky, pamäte a blokov multiplikátora. Tie sú obklopené programovateľnou smerovacou štruktúrou, ktorá umožňuje bloky naprogramovaním prepojiť. Pole je obklopené programovateľnými vstupno/výstupnými blokmi (I/O), ktoré spájajú čip s okolitým svetom.

Usporiadanie týchto blokov je špecifické pre konkrétneho výrobcu.

Každý FPGA sa opiera o základné programovacie technológie (ďalej už len technológie), ktoré slúžia na ovládanie programovateľných prepínačov. Tie dávajú FPGA ich programovateľnosť. Existuje niekoľko technológií a ich rozdiely majú významný vplyv na logické architektúry.

TECHNOLÓGIA PROGRAMOVANIA STATICKEJ PAMÄTE

Statické pamäťové články sú základom pre SRAM technológiu, ktorá je široko používaná a je možné ju nájsť v zariadeniach od výrobcov Xilinx, Lattice a Altera. V týchto zariadeniach, sú statické pamäťové články rozdelené v celom FPGA pre poskytovanie konfigurovateľnosti. Existujú dve primárne použitia SRAM článkov. Najčastejšie sa používajú na nastavenie vybratých riadkov pre multiplexory, ktoré riadia prepojenie signálov. Väčšina zostávajúcich SRAM článkov sa používa na ukladanie dát do vyhľadávacej tabuľky (LUT), ktoré sú bežne používané v SRAM implementovaných logických funkciách.

Technológia SRAM sa stala dominantnou pre FPGA, pretože jeho primárne výhody sú preprogramovateľnosť a používa štandardnú CMOS technológiu. Z praktického hľadiska sa články SRAM môžu neobmedzene programovať.

TECHNOLÓGIA PROGRAMOVANIA FLASH/EEPROM

Jednou alternatívou, ktorá rieši niektoré nedostatky SRAM technológie, je použiť technológiu pohyblivej brány, ktorá aplikuje poplatok na túto bránu. Tento prístup sa používa vo flash alebo EEPROM pamäťových článkov. Tieto články sú non-volatile, tzn. nestretia svoje informácie keď sa prístroj vypne.

Táto technológia programovania flash ponúka niekoľko jedinečných výhod, tá najdôležitejšia je non-volatilita. Táto vlastnosť eliminuje potrebu externých zdrojov na ukladanie a načítanie konfiguračných údajov. Navyše flash zariadenie môže fungovať hneď po zapnutí bez toho, aby bolo potrebné čakať na načítanie konfiguračných dát.

Nevýhodou flash zariadení je, že nemôžu byť preprogramované nekonečne veľakrát. Pre väčšinu použitia FPGA je však tento počet programovaní dostačujúci. V mnohých prípadoch sa FPGA programuje len na jedno použitie. Ďalšou nezanedbateľnou nevýhodou flash zariadení je potreba neštandardných CMOS procesov. Dnes sa už využíva kombinácia flash so SRAM technológiou.

TECHNOLÓGIA PROGRAMOVANIA ANTI-POISTKY

Alternatívou ku technológiám SRAM a pohyblivej brány je technológia antipoistky. Táto technológia je založená na štruktúrach, ktoré vykazujú za normálnych okolností veľmi vysokú odolnosť. Programovateľný prvok, antipoistka, je priamo používaný na prenos signálov FPGA. Tieto antipoistky sú tvorené formou sendviču z izolačného materiálu ako amorfný kremík alebo oxid kremičitý medzi dvoma vrstvami kovov.

Hlavnou výhodou technológie antipoistky je jej nízka plocha. Ďalšou výhodou antipoistiek je, že majú nižší odpor a parazitický kapacitný odpor ako iné technológie. Malá plocha, odolnosť a kapacitný odpor poistiek znamená, že je možné zahrnúť viac prepínačov v rámci zariadenia čo je praktické v iných technológiách.

Technológia programovania antipoistky má aj svoje nevýhody. Najmä antipoistky FPGA vyžadujú neštandardné CMOS. Okrem toho základný mechanizmus programovania, ktorý zahŕňa významné zmeny vlastností materiálov v poistkách, vedie k škálovateľným výzvam, kedy je zhodnotený nový IC výrobný proces.

Antipoistky sú nevhodné pre aplikácie kde sú konfiguračné zmeny potrebné pre svoju neschopnosť preprogramovania.

Všetky tri programovacie technológie skúmané v tejto časti sú používané v moderných zariadeniach avšak technológia SRAM sa stala najpoužívanejšou.

JAZYKY PRE SYNTÉZU HRADLOVÝCH POLÍ

V začiatkoch programovania hradlových polí sa pre návrh používali proprietárne jazyky (napr. ABEL). Dnes sa pre programovanie obsahu hradlových polí používajú jazyky VHDL a Verilog. Jednoduchšie návrhy je možné nakresliť aj pomocou grafického editoru.

VHDL (VHSIC Hardware Description Language) je jazyk pre popis hardvéru, ktorý sa používa na návrh a simuláciu digitálnych integrovaných obvodov, napríklad programovateľných hradlových polí (FPGA, CPLD, ...) alebo rôznych zákazníckych obvodov (ASIC). Môže byť použitý aj ako univerzálny paralelný programovací jazyk.

VHDL je štandardom IEEE od roku 1987, v roku 1997 bol revidovaný a je použiteľný aj pre návrh analógových obvodov. Ide o typovaný programovací jazyk. Má prostriedky pre popis paralelizmov, konektivity a explicitné vyjadrenie času.

Verilog je jazyk pre popis hardware (HDL), slúži na modelovanie a návrh elektronických systémov. Jazyk (niekedy nazývaný Verilog HDL) podporuje design, verifikáciu a realizáciu analógových, digitálnych a zmiešaných signálových obvodov s rôznou úrovňou abstrakcie. Návrhári Verilogu chceli jazyk so syntaxou podobnou programovaciemu jazyku C, pretože bol široko známy a kladne prijímaný. Jazyk má preprocesor ako C a hlavné kľúčové slová (if/else, while, atď). Mechanizmus formátovania a priorita operátorov je taktiež podobná.

Jazyk Verilog sa líši v niekoľkých základných bodoch. Pri deklarácii konštánt je potrebné pridať ich šírku v bitoch. Nemá štruktúry, ukazovateľov alebo rekurzívne rutiny.

Späť Hore